214 Глава 5. Память

типами ОЗУ (поп-volatile memory): большей емкостью, низким энергопотреблением, более высоким быстродействием и невысокой себестоимостью хранения единицы информации.

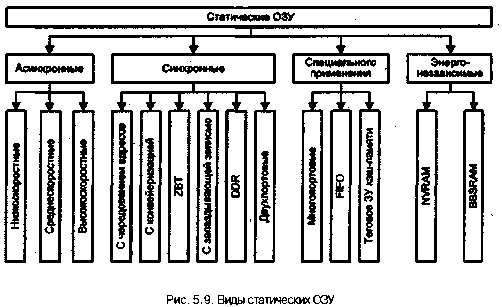

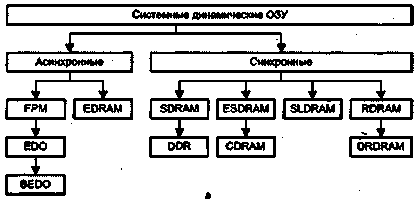

Энергозависимые ОЗУ можно подразделить на две основные подгруппы: динамическую память (DRAM — Dynamic Random, Access Memory) и статическую память (SRAM — Static Random Access Memory). '

Статическая и динамическая оперативная память

В статических ОЗУ запоминающий элемент может хранить записанную информацию неограниченно долго (при наличии питающего напряжения). Запоминающий элемент динамического ОЗУ способен хранить информацию только в течение достаточно короткого промежутка времени, после которого информацию нужно восстанавливать заново, иначе она будет потеряна. Динамические ЗУ, как и статические, энергозависимы.

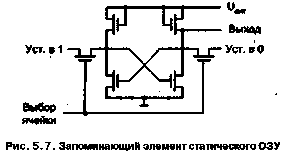

Роль запоминающего элемента в статическом ОЗУ исполняет триггер. Такой триггер представляет собой схему с двумя устойчивыми состояниями, обычно состоящую из четырех или шести транзисторов (рис. 5.7). Схема с четырьмя транзисторами обеспечивает большую емкость микросхемы, а следовательно, меньшую стоимость, однако у такой схемы большой ток утечки, когда информация просто хранится. Также триггер на четырех транзисторах более чувствителен к воздей-. ствию внешних источников излучения, которые могут стать причиной потери информации. Наличие двух дополнительных транзисторов позволяет в какой-то мере компенсировать упомянутые недостатки схемы на четырех транзисторах, но, главное — увеличить быстродействие памяти.

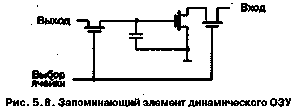

Запоминающий элемент динамической памяти значительно проще. Он состоит из одного конденсатора и запирающего транзистора (рис. 5.8).