232 Глава5. Память

Микросхемы 3D-RAM. Этот тип памяти разработан совместно компаниями Mitsubishi и Sun Microsystems с ориентацией на трехмерные графические ускорители. Помимо массива запоминающих элементов, микросхема 3D-RAM (трехмерная RAM) содержит процессор (арифметико-логическое устройство) и кэш-память. Процессор позволяет выполнять некоторые операции с изображением прямо в памяти. Основные преобразования над пикселами реализуются за один такт, поскольку стандартная последовательность действий «считал, изменил, записал» сводится к одной операции — «изменить», выполняемой в момент записи. Процессор микросхемы позволяет за секунду выполнить около 400 млн операций по обработке данных и закрасить до 4 млн элементарных треугольников. Кэш-память обеспечивает более равномерную нагрузку на процессор при интенсивных вычислениях. Ядро 3D-RAM состоит из четырех банков общей емкостью 10 Мбит. Размер строк памяти выбран таким, чтобы в пределах одной и той же области памяти находилось как можно больше трехмерных объектов. Это дает возможность сэкономить время на переходы со строки на строку. По цене данный тип микросхем сравним с VRAM.

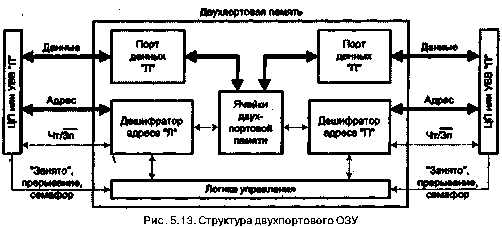

Многопортовые ОЗУ

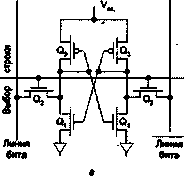

Стандартное однопортовое ОЗУ имеет по одной шине адреса, данных и управления и в каждый момент времени обеспечивает доступ к ячейке памяти только одному устройству. Структура запоминающего элемента (ЗЭ) такого ОЗУ приведена на рис. 5.12, а.

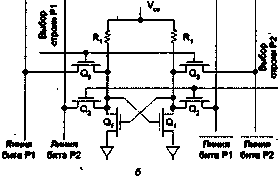

Рис. 5.12. Запоминающие элементы статического ОЗУ: а — однопортового;

б — двухп о рто во го

В отличие от стандартного в я-портовом ОЗУ имеется п независимых наборов шин адреса, данных и управления, гарантирующих одновременный и независимый доступ к ОЗУ п устройствам. Данное свойство позволяет существенно упростить создание многопроцессорных и многомашинных вычислительных систем, где многопортовое ОЗУ выступает в роли общей или совместно используемой памяти. В рамках одной ВМ подобное ОЗУ может обеспечивать обмен информацией между ЦП и УВВ (например, контроллером магнитного диска) намного эффективней, чем прямой доступ к памяти. В настоящее время серийно выпускаются