2 6 2 Глава 5. Память

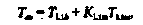

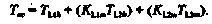

Среднее время доступа Г„ к одноуровневой кэш-памяти можно оценить как:

где 7*ш — 1время обращения при попадании; KLtm— коэффициент промахов; Тщ* ~~ потери на промах. Для двухуровневой кэш-памяти имеем:

Потенциальная экономия за счет применения L2 зависит от вероятности попаданий как в L1, так и в L2. Ряд исследований показывает, что использование кэшпамяти второго уровня существенно улучшает производительность.

В большинстве семейств микропроцессоров предусмотрены специальное ИМС контроллеров внешней кэш-памяти, например микросхема 8291 для микропроцессора Intel 486 или 82491 — для Intel Pentium. Для ускорения обмена информацией между ЦП и L2 между ними часто вводят специальную шину, так называемую шину заднего плана, в отличие от шины переднего плана, связывающей ЦП с основной памятью.

Количество уровней кэш-памяти не ограничивается двумя. В некоторых ВМ уже можно встретить кэш-память третьего уровня (L3) и ведутся активные дискуссии о введении также и кэш-памяти четвертого уровня (L4). Характер взаимодействия очередного уровня с предшествующим аналогичен описанному для L1 и L2. Таким образом, можно говорить об иерархии кэш-памяти. Каждый последующий уровень характеризуется большей емкостью, меньшей стоимостью, но и меньшим быстродействием, хотя оно все же выше, чем у ЗУ основной памяти.

Дисковая кэш-память

Концепция кэш-памяти применима и к дисковым ЗУ. Принцип кэширования дисков во многом схож с принципом кэширования основной памяти, хотя способы доступа к диску и ОП существенно разнятся. Если время обращения к любой ячейке ОП одинаково, то для диска оно зависит от целого ряда факторов. Во-первых, нужно затратить некоторое время для установки головки считывания/записи на нужную дорожку. Во-вторых, поскольку при движении головка вибрирует, необходимо подождать, чтобы она успокоилась. В-третьих, искомый сектор может оказаться под головкой также лишь спустя некоторое время.

Дисковая кэш-память представляет собой память с произвольным доступом, «размещенную» между дисками и ОП. Емкость такой памяти обычно достаточно велика — от 8 Мбайт и более. Пересылка информации между дисками и основной памятью организуется контроллером дисковой кэш-памяти. Изготавливается дисковая кэш-память на базе такихже полупроводниковых запоминающих устройств, что И основная память, поэтому в ряде случаев с ней обращаются как с дополнительной основной памятью. С другой стороны, в ряде операционных систем, таких как UNIX, в качестве дискового кэша используется область основной памяти.

В дисковой кэш-памяти хранятся блоки информации, которые с большой вероятностью будут востребованы в ближайшем будущем. Принцип локальности, обеспечивающий эффективность обычной кэш-памяти, справедлив и для дисковой, приводя к сокращению времени ввода/вывода данных от величин 20-30 мс до значений порядка 2-5 мс, в зависимости объема передаваемой информации.