Модель устройства управления 295

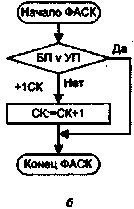

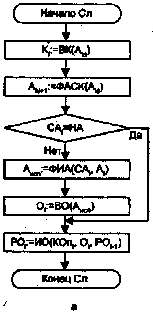

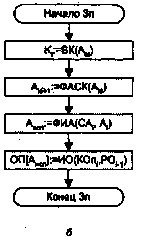

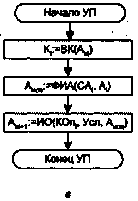

Рис. 6.1 .Типовые граф-схемы этапов исполнения команды: а — «Сложение»; б — «Запись»;

в— «Условный переход»

Оператор этапа исполнения операции для команд "Зп" имеет смысл записи результата предыдущей операции Р0М в ячейку с адресом Аисп:

0П[Аисл]:=ИО(КОП(,РОм).

Местоположение Р0М определяется кодом операции ΚΟη. Оператор этапа ИО для команд «УП» обеспечивает формирование адреса следующей (i + 1)-й команды в зависимости от Аисп и значения проверяемого условия перехода Уел

Местоположение проверяемого условия также определяется кодом операции КЩ

I

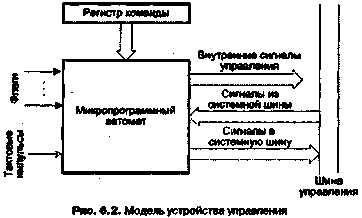

Модель устройства управления

Для выполнения своих функций УУ должно иметь входы, позволяющие определить состояние управляемой системы, и выходы, через которые реализуется управление поведением системы. Модель УУ показана на рис. 6.2 [200]. Входной информацией для устройства управления служат:

• тактовые импульсы — с каждым тактовым импульсом УУ инициирует выполне-

ние одной или нескольких микроопераций;

• код операции — код операции текущей команды поступает из регистра команды и используется, чтобы определить, какие микрооперации должны выполняться в течение машинного цикла;