|

|

|

|

|

|

|

|

|

|

Микропрограммный автомат с программируемой логикой 3 2 3

|

|

|

|

|

|

|

|

• определить множество неизбыточных решений и их цену;

• выбрать в качестве окончательного решения неизбыточное решение с минимальной ценой.

Для нахождения неизбыточных решений годится такая же процедура. Для каждого избыточного решения бета j строится таблица покрытий наподобие табл. 6.4, однако в ее столбцах записываются только МКН, соответствующее решению бета. Затем, используя описанные выше эвристические методы, получают сокращенную таблицу покрытий, из которой простым перебором или методом Петрика находятся все неизбыточные решения.

Пути повышения быстродействия автоматов микропрограммного управления

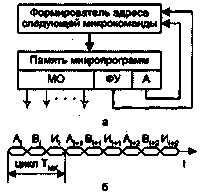

Цикл выполнения микрокоманды Гмк можно представить в виде трех этапов:

• формирования адреса очередной микрокоманды в ФАМ (А);

• выборки по данному адресу микрокоманды из памяти микропрограмм (Bj);

• исполнения микрокоманды в операционной (ОЧ) или адресной части (АЧ) вычислительной машины (И).

Порядок следования этапов определяется способом соединения формирователя адреса следующей микрокоманды и памяти микропрограмм.

Структура МПА (рис. 6.22, а) с ФАМ и ПМП, связанными непосредственно друг с другом, не допускает совмещения этапов во времени — здесь этап +1 начинается только после выполнения этапа Д(рис. 6.22, б).

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 6.22. Построение МПА без совмещения: а — структурная схема; б— временная диаграмма обработки микрокоманд

В течение цикла Гмк все узлы заняты обработкой только одной, текущей микрокоманды с номером i, причем последовательный характер обработки МКне позволяет достичь высокого быстродействия:

Производительность ВМ повышается при одновременной конвейерной обработке в МПА нескольких микрокоманд, находящихся на различных этапах выпол-

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

324 Глава 6. Устройства управления

|

|

|

|

|

|

|

|

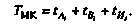

нения. Для совмещения во времени этапов А{ В^И.Ь МПА вводятся дополнительные запоминающие, элементы, которые хранят результаты обработки на каждом этапе.

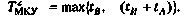

В МПА с одним уровнем совмещения Используется один запоминающий элемент — конвейерный регистр микрокоманды, подключенный к выходу памяти микропрограмм (рис. 6.23, а). В данной структуре реализуется одновременная обработка двух микрокоманд: в то время как исполняется находящаяся в РМК i-я микрокоманда (этап И{), в ФАМ вычисляется адрес (i + 1)-й микрокоманды (этап +|), и затем по этому адресу из ПМП выбирается (i + 1)-я микрокоманда (этап 5,+(). Следовательно, в МПА с одним уровнем совмещения обеспечивается параллельное выполнение этапов +l_rri и Bi+i и этапа,__, (рис, 6,23, б): ?мк = тах{(^ + ίΒ), ί„}.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 6.23. Построение МПАс одним уровнем совмещения: а —структурная схема; б — временная диаграмма обработки микрокоманд

|

|

|

|

|

|

|

|

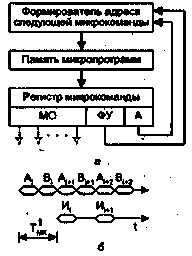

Очевидно, что при t„ < tA + tB в данной структуре наблюдается вынужденный простой операционной (или адресной) части ВМ. Этот недостаток устраняется в МПА с двумя уровнями совмещения (рис. 6.24, а), в котором ФАМ и ПМП связаны друг с другом двумя конвейерными регистрами — РМК и РАМ. Здесь одновременно обрабатываются три микрокоманды: в операционной или адресной части исполняется MKt (этап HJ выбирается из памяти МКт (этап В/+1),а в ФАМ вычисляется адрес МК^ (этап Ai&2). Как видно из рис. 6.24, б, в такой структуре совмещается во времени выполнение всех трех этапов и Т&к = u\ax{tA, tR, tM).

Методы конвейерной обработки обеспечивают значитетяши выигрыш только при выполнении линейных участков микропрограммы. Если реализуемая в ФАМ функция управления является условной, а значение условия вырабатывается на текущем этапе в операционной (адресной) части, то правильный адр следующей микрокоманды может быть вычислен только по окончании этапа К, ответственного

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Контрольные вопросы 3 2 5

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 6.24. Построение МПА с двумя уровням и совмещения: а — структурная схема; б— временная диаграмма обработки микрокоманд

за выработку значения условия перехода. В итоге длительность цикла для МПА с одним уровнем совмещения увеличивается до величины

а для МПА с двумя уровнями совмещения — до величины

а для МПА с двумя уровнями совмещения — до величины

Всего, в зависимости от использования регистров — регистра РМК, состоящего из адресной и микрооперационной частей, регистра РАМ, регистра состояния РГС (для хранения условия перехода), — можно сформировать 11 различных структур МПА Эти структуры, их временные диаграммы и оценки эффективности приведены в [32, с. 184-212]. Там же показано, что выбор оптимальной структуры определяется особенностями конкретной микропрограммы.

Контрольные вопросы

1. Охарактеризуйте основные функции устройства управления.

2. Какие аргументы и результат имеет функция ЦФ-ВК?

3. Какие аргументы и результат имеет функция ЦФ-ФАСК?

|

|

|

|

|

|

|

|

|

|