Структуры операционных устройств 331

а третье — суммарную стоимость комбинационных схем, реализующих микрооперации Ктипов над N словами.

Затраты времени на выполнение операций типа «сложение» в ОПУ с жесткой

структурой равны

где ίΒ — длительность микрооперации выдачи операндов из регистров; tc— продолжительность микрооперации «сложение»; tn — длительность микрооперации приема результата в регистр.

Достоинством ОПУ с жесткой структурой является высокое быстродействие, недостатком — малая регулярность структуры, что затрудняет реализацию таких ОПУ в виде больших интегральных схем.

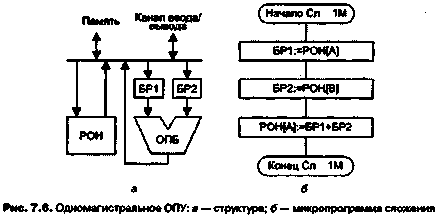

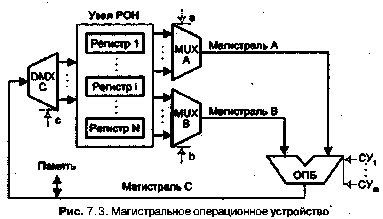

Операционные устройства с магистральной структурой

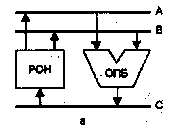

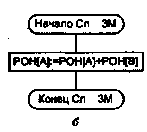

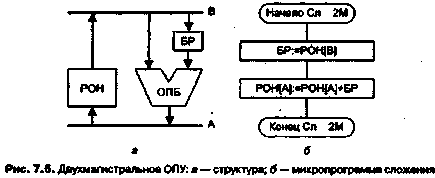

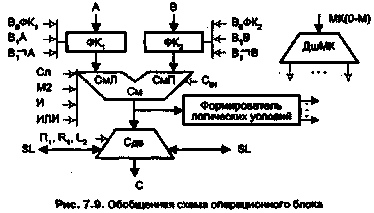

В ОПУ с магистральной структурой все внутренние регистры объединены в отдельный узел регистров общего назначения (РОН)1, а все комбинационные схемы — в операционный блок (ОПБ), который зачастую ассоциируют с термином «арифметико-логическое устройство».

Операционный блок и узел регистров сообщаются между собой с помощью , магистралей — отсюда и название «магистральное ОПУ».

Пример магистрального ОПУ представлен на рис. 7.3.

В состав узла РОН здесь входят N регистров общего назначения, подключаемых к магистралям А и В ^ерез мультиплексоры MX А и MX В. Каждый из мультиплексоров является управляемым коммутатором, соединяющим выход одного из РОН с соответствующей магистралью. Номер подключаемого регистра определяется адресом а или Ь, подаваемым на адресные входы мультиплексора из устройства управления.

В операционных устройствах для обработки чисел с плавающей запятой вместо РОН часто используется отдельный узел регистров с плавающей запятой.

— количество микроопераций, реализуемых ОПУ с жесткой

— количество микроопераций, реализуемых ОПУ с жесткой