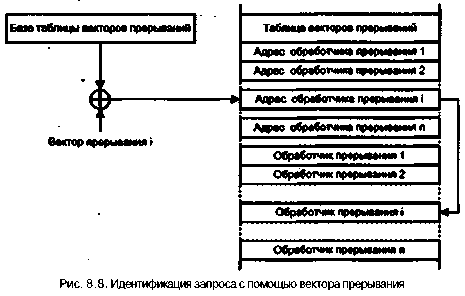

При цепочечном методе для передачи запроса прерывания модули ввода/вывода совместно используют одну общую линию. Линия подтверждения прерывания последовательно проходит через все МВБ. Когда ЦП обнаруживает запрос прерывания, он посылает сигнал по линии подтверждения прерывания. Этот сигнал двих жется через цепочку модулей, пока не достигнет того, который выставил запрос. Запросивший модуль реагирует путем выдачи на шину данных своего вектора прерывания.

В варианте арбитража шины МВБ, прежде чем выставить запрос налинии запроса прерывания, должен получить право на управление шиной. Таким образом, в каждый момент времени активизировать линию запроса прерывания может только один из модулей. Когда ЦП обнаруживает прерывание, он отвечает по линии подтверждения. После этого запросивший модуль помешает на шину данных свой вектор прерывания.

Перечисленные методы служат не только для идентификации запросившего МВБ, но и для назначения приоритетор, когда прерывание запрашивают несколько устройств. При множественных линиях запроса ЦП начинает с линии, имеющей наивысший приоритет. В варианте программной идентификации приоритет модулей определяется очередностью их проверки. Для цепочечного метода приоритет модулей определяется порядком их следования в цепочке. Порядок задания приоритетов при арбитраже был рассмотрен ранее в главе 4.

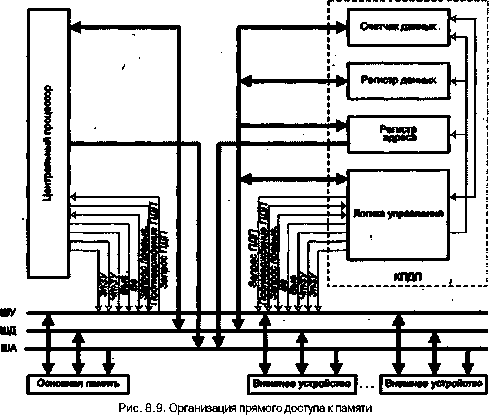

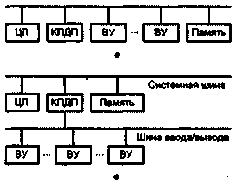

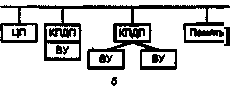

Прямой доступ к памяти

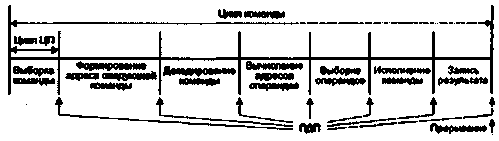

Хотя ввод/вывод по прерываниям эффективнее программно управляемого, оба этих метода страдают двумя недостатками:

- темп передачи при вводе/выводе ограничен скоростью, с которой ЦП в состоянии опросить и обслужить устройство;