45 0 Глава 9. Основные направления в архитектуре процессоров

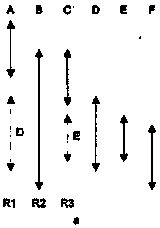

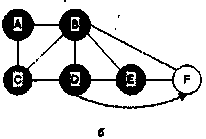

вательность активного вовлечения в выполнение каждого виртуального регистра (рис. 9.37, а) и раскрашенный граф (рис. 9-37, б).

Как видно, не удалось раскрасить только виртуальный регистр F, его придется отображать на ячейку памяти.

Аппаратная оптимизация использования регистров в RISC-процессорах ориентирована на сокращение затрат времени при работе с процедурами. Наибольшее время в программах, написанных на ЯВУ, расходуется на вызовы процедур и возврат из них. Связано это с созданием и обработкой большого числа локальных переменных и констант. Одним из механизмов для борьбы с этим эффектом являются так называемые,регистровые окна. Главная их задача — упростить и ускорить передачу параметров от вызывающей процедуры к вызываемой и обратно.

Рис. 9.37. Иллюстрация методараскраски графа: а — временная последовательность

активногоиспользованиявиртуальныхрегистров; б— граф взаимного

использования регистров

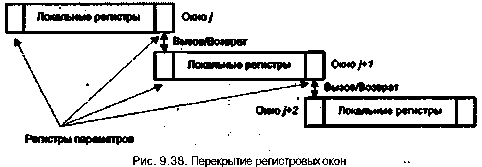

Регистровый файл разбивается на группы регистров, называемые окнами. Отдельное окно назначается глобальным переменным. Глобальные регистры доступны всем процедурам, выполняемым в системе в любое время. С другой стороны, каждой процедуре выделяется отдельное окно в регистровом файле. Все окна имеют одинаковый размер (обычно по 32 регистра) и состоят из трех полей. Левое поле каждого регистрового окна одновременно является и правым полем предшествующего ему окна (рис. 9.38). Среднее поле служит для хранения локальных переменных и констант процедуры.

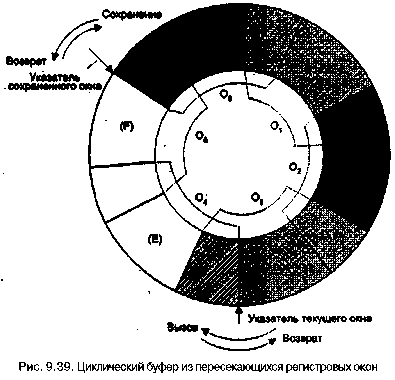

База окна (первый в последовательности регистров окна) указывается полем, называемым указателем текущего окна (CWP, Current Window Pointer), обычно расположенным в регистре (слове) состояния ЦП. Если текущей процедуре назначено регистровое окно j CWP содержит значение j

Каждой вновь вызванной процедуре выделяется регистровое окно, непосредственно следующее за окном вызвавшей ее процедуры. Последние £ регистров окна; одновременно являются первыми к регистрами OKHaj + 1. Если процедура, занимающая окно j обращается к процедуре, которой в данной архитектуре должно быть назначено окно j + 1, она может передать в процессе вызова к аргументов.